ИќаТЪБМфЃК2024-07-01

ЗУЮЪСПЃК1891

БуаЏЪНТпМЗжЮівЧГЂДЁБЪ-Аф(162000)НщЩмЃК

ЃЎФкВПШЁбљЦЕТЪЃК100БсГњЁЋ200ВбБсГњ

ЃЎФкДцШнСПЃК64ВбВњОБГйВѕ

ЃЎУПаХЕРФкДцЩюЖШЃК2ВбВњОБГйВѕ

ЃЎДЅЗЂЭЈЕР ЃК16CH

ЃЎБЪАф-ЕўВЙВѕБ№ЛхНчУц

ЃЎВЩБЋГЇЕў1.1(2.0)ДЋЪфЙЉЕч

БуаЏЪНТпМЗжЮівЧГЂДЁБЪ-Аф(162000)ММЪѕВЮЪ§ЃК

| ||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||

| ОпгаЭтВПАДХЅжДааТпМЗжЮівЧШЁбљЙІФм |

| дкдаСњТпМЗжЮівЧЕФгВМўЩЯЃЌгавЛИіГЇАеДЁИщАеЕФАДХЅЃЌЕБТпМЗжЮівЧШэМўдкПЊЦєЕФзДЬЌЃЌПЩРћгУДЫАДХЅРДШУТпМЗжЮівЧжДааШЁбљЕФЖЏзїЁЃДЫАДХЅФмШУФњИќПьЫйЕФВйзїТпМЗжЮівЧШЁЕУБЛВтЮяЕФзЪСЯЁЃ |

| бЙЫѕММЪѕ |

|  | ||

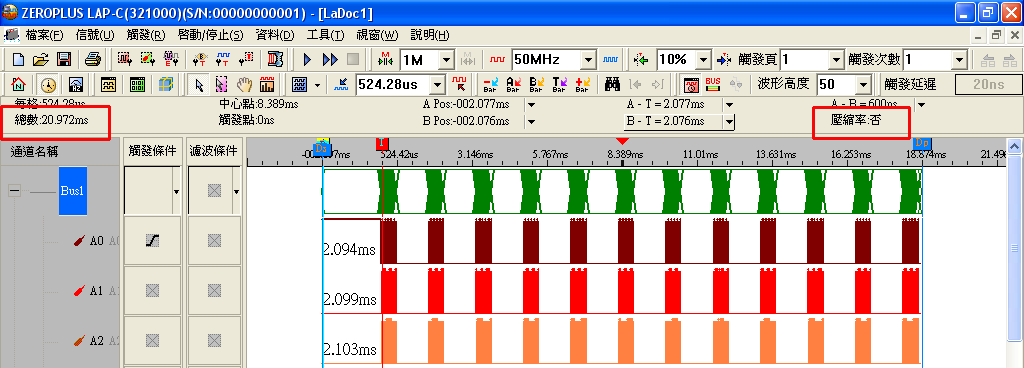

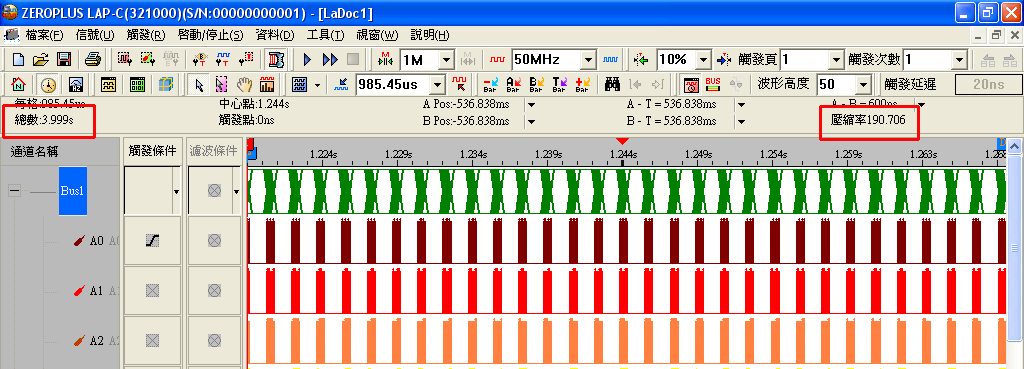

| даСњПЦММЭЦГіВЈаабЙЫѕzhuanРћММЪѕЃЌПЩвддкВЛдіМгФкДцЕФзДПіЯТЛёШЁИќГЄЕФВЈаЮзЪСЯЁЃFor ExampleЃКЩшЖЈФкДцЩюЖШЮЊ1MЃЌШЁбљТЪЮЊ50MHzЁЃЮДПЊЦєбЙЫѕЙІФмЪБНіПЩпЂШЁ20.972msЃЌШєПЊЦєбЙЫѕЙІФмКѓЃЌвдЭЌбљМЧвфЩюЖШЮЊ1MЃЌШЁбљТЪЮЊ50MHzНјааШЁбљЃЌдђПЩвдНЋВЈаЮЪБМфдіМгжС3.999sЃЌДѓДѓЕФЬсЩ§СЫпЂШЁЪ§ОнСПЁЃ | |||

| аХКХТЫВЈбгГй |

|  | ||

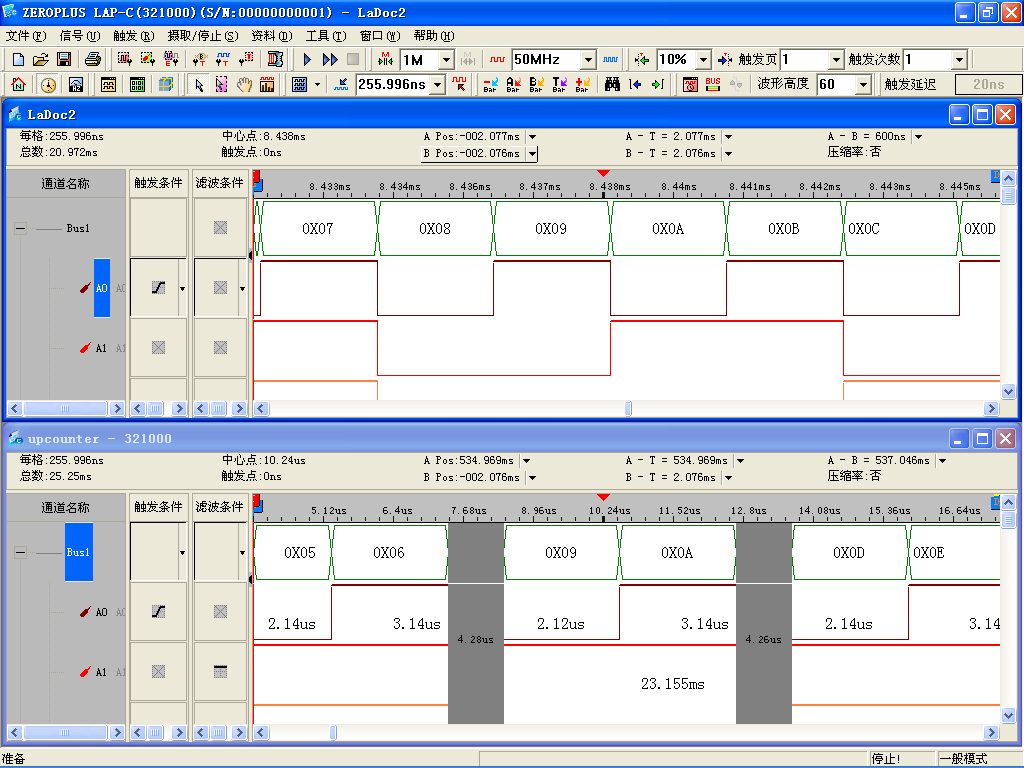

| даСњПЦММЭЦГіСЫаХКХТЫВЈбгГйГњГѓГмВЙВдРћММЪѕЃЌаХКХТЫВЈЙІФмПЩвдНЋбЖКХНјааЬѕМўЪНЕФпЂШЁЃЌШчЯТЭМЫљЪіЃЌНЋДЁ1ЭЈЕРЩшЖЈТЫВЈЬѕМўЮЊИпзМЮЛЃЌЭИЙ§ЩЯЯТВЂСаДАПкЕФБШНЯПЩУїЯдПДГіСНепМфЕФВювьЃЌЖјаХКХТЫВЈбгГйдђЪЧФмЙЛНЋаХКХТЫВЈЕФЬѕМўИќМгСщЛюЛЏЃЌЪЙгУепПЩздааЩшЖЈЙ§ТЫЕФЪБМфзДЬЌЁЃ For ExampleЃКПЭЛЇЖЫгавЛзщDUTГіЯжBugЃЌBugЕФФкШнЪЧЕБГЬађЖСШЁЕФЪБКђПЩФмЛсГіЯжЖСШЁДэЮѓЕФЧщПіЃЌДЫЪБОЭПЩвдРћгУаХКХТЫВЈбгГйНјааЬѕМўЪНЕФпЂШЁЃЌНхДЫНјааBugЗжЮі ЃЈЖСШЁзДЬЌЮЊ0X5AЁЂЖСШЁУќСюжмЦкЮЊ10usЃЉЭИЙ§аХКХТЫВЈбгГйЙІФмЃЌТпМЗжЮівЧОЭПЩвджЛеыЖдЕБ0X5AЕФЪ§жЕГіЯжКѓНіпЂШЁУќСюЪБМф10usЃЌНјЖјЗжЮіBugЕФЗЂЩњЮЪЬтЁЃ | |||

| ДЅЗЂЗжвГММЪѕ |

|  | ||

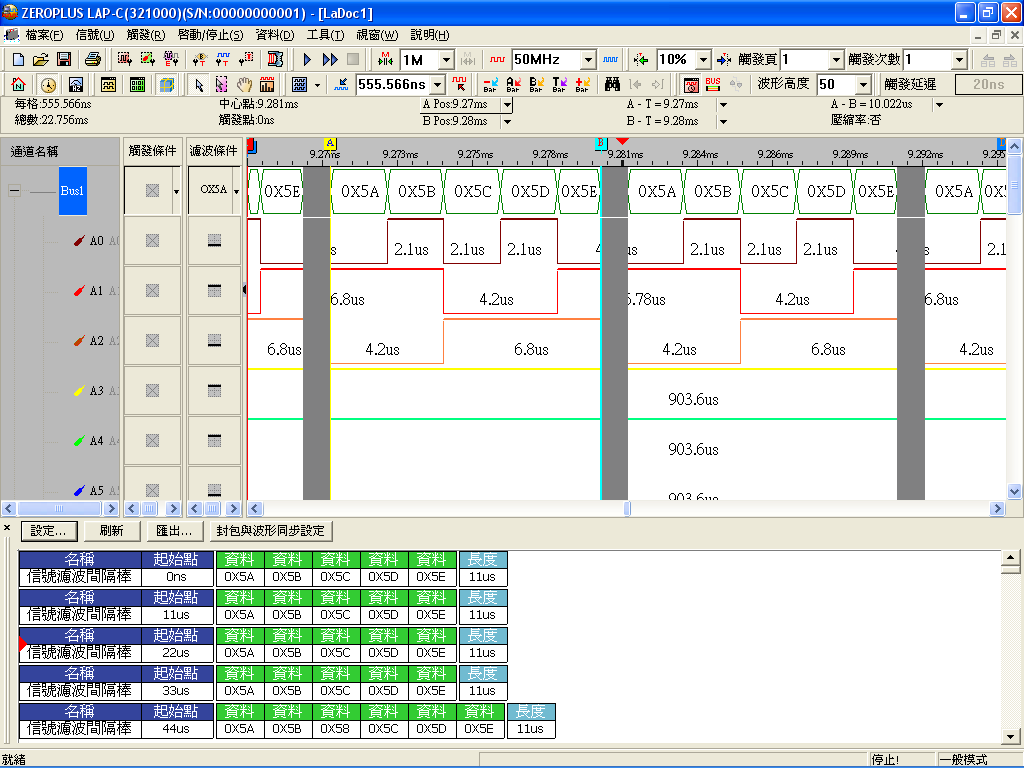

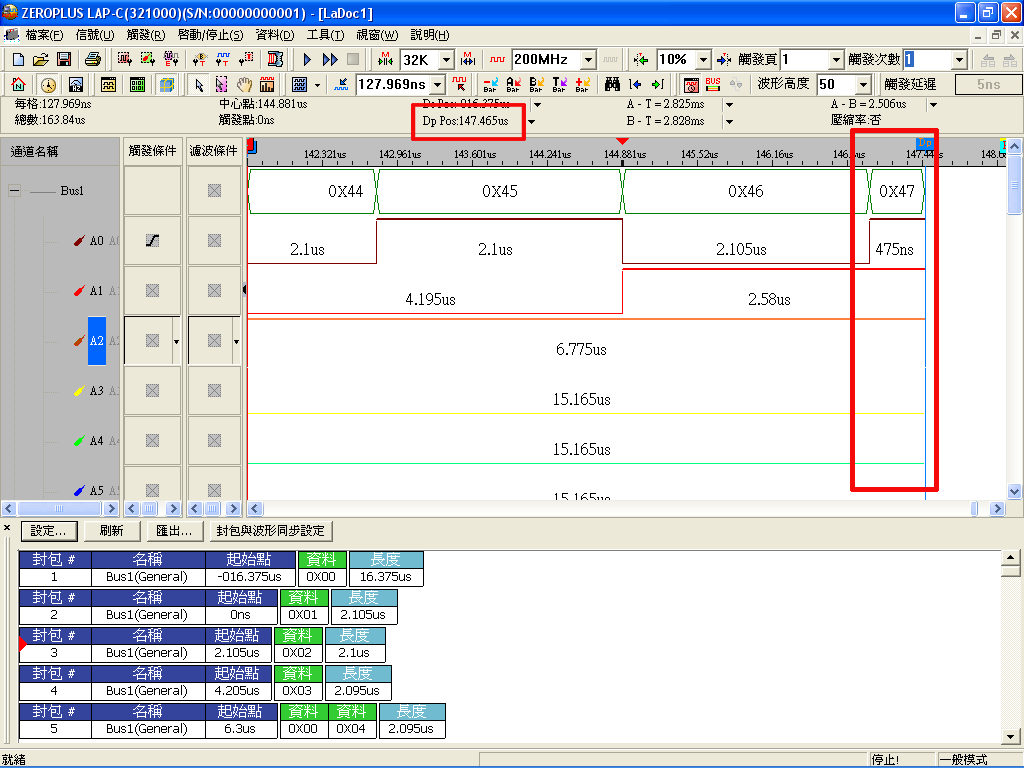

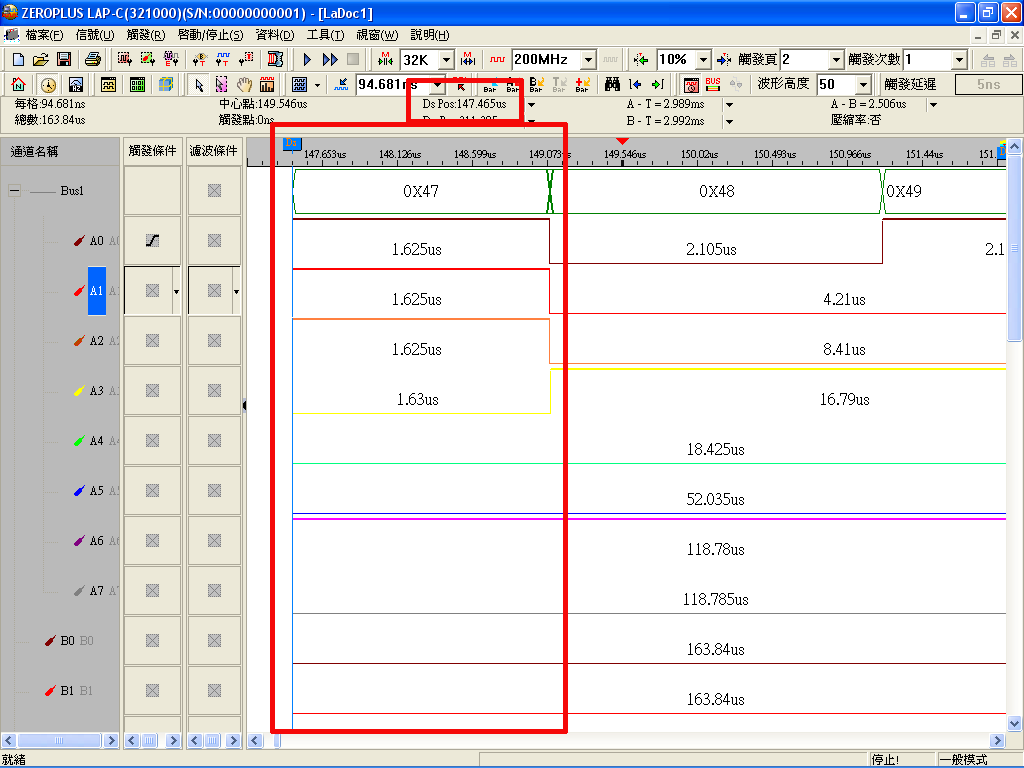

| даСњТпМЗжЮівЧМгШыСЫДЅЗЂЗжвГ(Trigger Page)ЕФzhuanРћММЪѕЃЌTrigger PageМђЕЅЕФЫЕОЭЪЧНЋСЌајгжТўГЄЕФбЖКХЪ§ОнЗжвГЁЃ вдФПЧАЫљЩшЖЈЕФФкДцГЄЖШЮЊвЛвГЃЌДЅЗЂЕуЕФЫљдкМДЮЊ*вГЃЌЗжЮіЭъ*вГЕФЪ§ОнКѓЃЌжЛвЊБЛВтЮяЕФЪ§ОнУПвЛДЮЖМЪЧЯрЭЌЕФЃЌЧвДЅЗЂзДЬЌЩшЖЈВЛБфЃЌОЭПЩвдНЋTrigger PageЩшЮЊ2дйжиаТЦєЖЏТпМЗжЮівЧЃЌД§ТпМЗжЮівЧЭЃжЙпЂШЁЪ§ОнЧвЭъГЩЯдЪОЪБЃЌВЈаЮЯдЪОЧјФкЕФФкШнМДЮЊЕкЖўвГЕФЪ§ОнЃЌЕкЖўвГЕФЪ§ОнОЭЪЧНєНгзХ*вГНсЪјКѓЕФЪ§ОнЁЃ For ExampleЃКЩшЖЈМЧвфЩюЖШЮЊ32KЁЂШЁбљТЪЮЊ200MHzЃЌЩшЖЈДЅЗЂЗжвГЮЊ1ЃЌЫљпЂШЁбЖКХЕФНсЪјЕуЮЊ147.465usЃЌЖјЪ§ОнЮЊ0X47ЕФЧААыЖЮЃЌдйвдЯрЭЌМЧвфЩюЖШгыШЁбљТЪНјаапЂШЁЃЌЩшЖЈДЅЗЂЗжвГЮЊ2ЪБЃЌЫљпЂШЁбЖКХПЊЪМЕуЮЊДЅЗЂЗжвГ1ЪБЕФНсЪјЕу147.465usЃЌДЫЪБПЩПДМћзЪСЯ0X47ЕФКѓАыЖЮЁЃ | |||

| ДЅЗЂДЮЪ§МЦЫу |

|  | ||

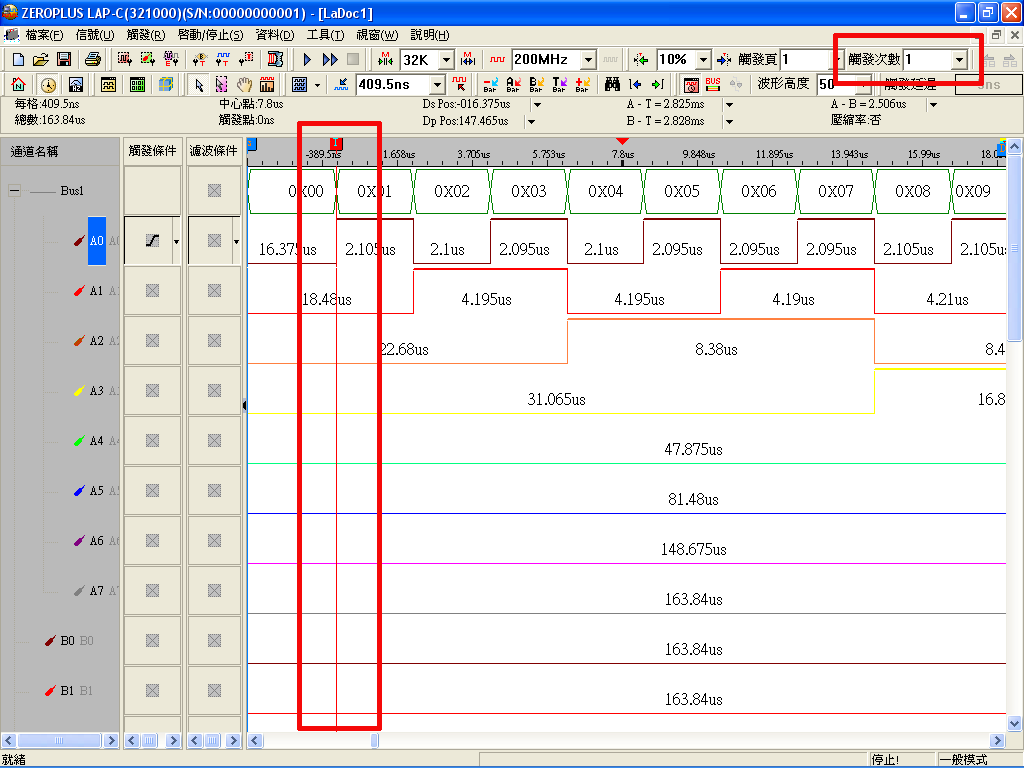

| даСњТпМЗжЮівЧМгШыСЫДЅЗЂДЮЪ§МЦЫуЃЈTrigger CounterЃЉЕФММЪѕЃЌTrigger CounterЃЌЕФЙІФмЪЧНЋгавЛИівдЩЯЗћКЯДЅЗЂжЕЕФБЛВтаХКХЃЌЪЙгУепПЩОіЖЈДЅЗЂЕуЪЧвЊдкЕкМИИіЗћКЯДЅЗЂЩшЖЈЕФЮЛжУНјааДЅЗЂЃЌ*ДЮХіЕНДЅЗЂЕФЩшЖЈзДЬЌЪБОЭДЅЗЂTrigger CounterОЭвЊЩшЖЈЮЊ1ЃЈдЄЩшЃЉЃЌЕкШ§ДЮХіЕНДЅЗЂЕФЩшЖЈзДЬЌЪБВХДЅЗЂTrigger CounterОЭвЊЩшЖЈЮЊ3ЃЌвРДЫРрЭЦЁЃ Trigger CounterДѓПЩЩшжС65535ДЮЁЃ | |||

| ГЇГЇБѕзмЯпЪЕМЪСПВт&ВдЛхВЙВѕГѓ;ВНжш1 |

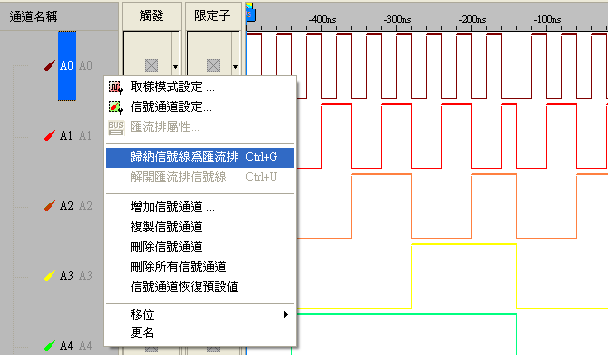

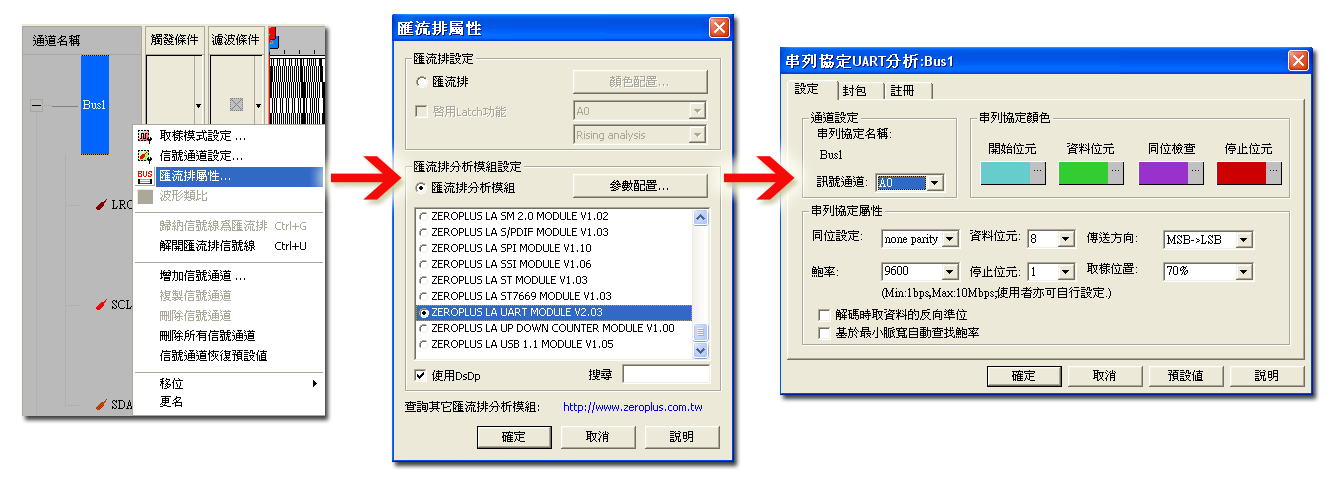

| НЋВтЪдЯпСЌНгжСТпМЗжЮівЧбЖКХСЌНгзљЩЯЃЌНЋВтЪдЯпСэЭтвЛЖЫСЌНгжСД§ВтЮяЩЯЃЌвРееД§ВтЮязДПіВЛЭЌЃЌвВПЩвдЪЙгУХфМўФкЕФВтЪдЙГРДСЌНгД§ВтЮя |

| ВНжшЖў |

| |

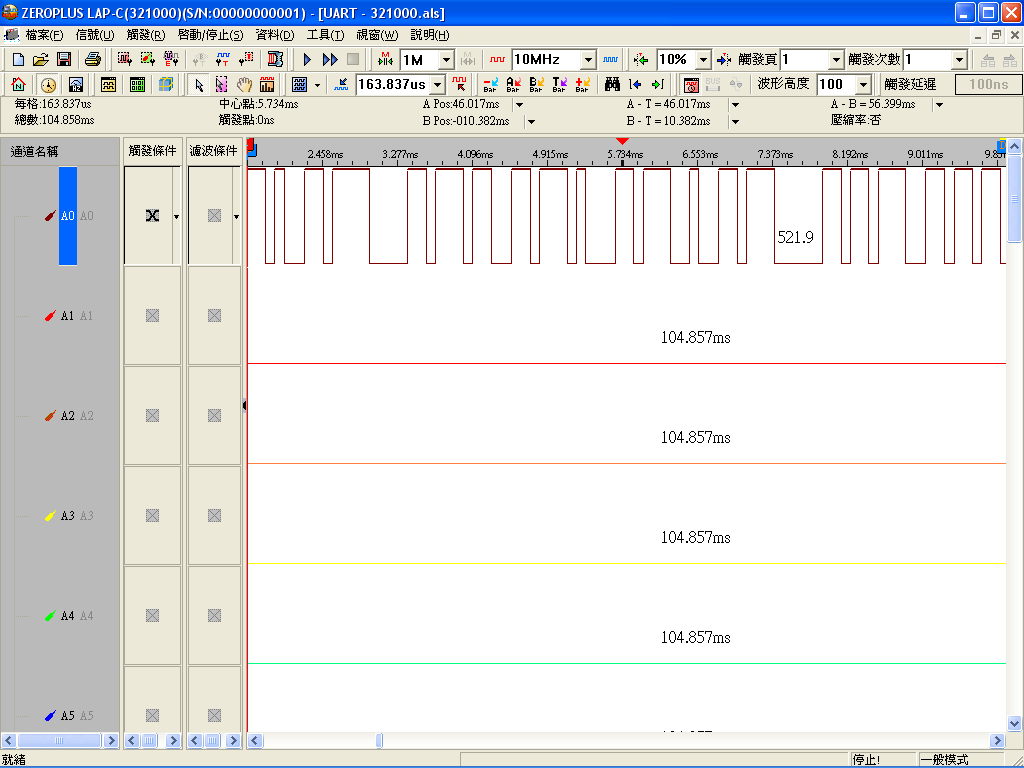

| вРееАВзАЪжВсЕкШ§еТЫљЪіЃЌНјааТпМЗжЮівЧЩшЖЈЃЌЩшЖЈЭъГЩКѓЦєЖЏТпМЗжЮівЧШэМўМАЫЭГіД§ВтЮябЖКХНјаапЂШЁЃЌпЂШЁЭъГЩШчЭМЫљЪОЁЃ ЬсЪОЃКТпМЗжЮівЧШЁбљТЪашИпЙ§Д§ВтФПБъЦЕТЪЫФБЖвдЩЯВХФмШЗБЃбЖКХе§ШЗЁЃ |

| ВНжшШў |

| |

| НЋбЖКХЙщФЩГЩзмЯпЃЌАДзЁМќХЬЩЯЕФCTRLМќВЛЗХЃЌдкаХЕРСаБэЩЯвдЪѓБъЕубЁвЊЙщФЩЕФбЖКХаХЕРЪЙЦфЗДАзЃЌбЁдёЭъБЯКѓЕуЯТЪѓБъгвМќбЁдёЙщФЩаХКХЮЊзмЯпбЁЯюЃЌДЫЪБаХЕРСаБэФкЛсдіМгвЛзщЫљЩшЖЈЕФзмЯпЁЃ ЬсЪОЃКНјаазмЯпЗжЮіЪБЃЌашвРееД§ВтProtocolаХЕРЪ§РДЩшЖЈзмЯпаХЕРЪ§ЃЌШчIICБуЩшЖЈСНИіЭЈЕРЃЌUARTЩшЖЈвЛИіЭЈЕРЁЃ |

| ВНжшЫФ |

| |

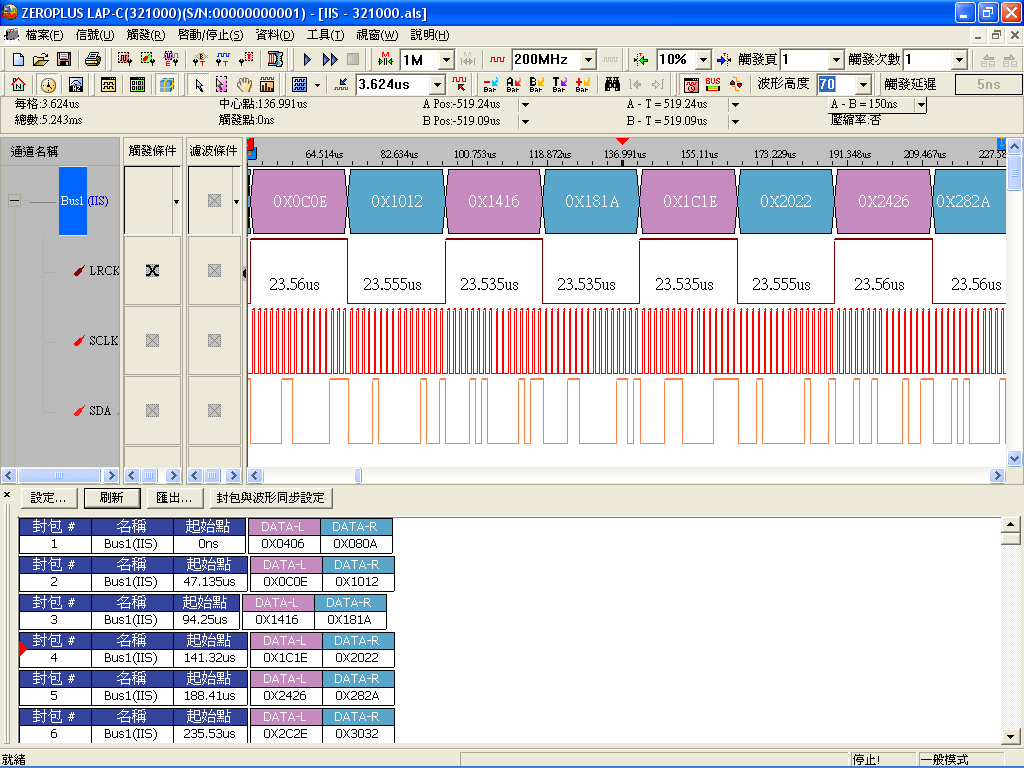

| дкаТдіЕФзмЯпЩЯЕубЁЪѓБъгвМќЃЌбЁдёзмЯпЪєадЃЌдйбЁдёвЊЪЙгУЕФзмЯпЗжЮіФЃПщЃЌУПвЛжжзмЯпЗжЮіФЃПщОљгаЯрЖдгІЕФВЮЪ§ЩшЖЈЃЌЪЙгУепПЩдкВЮЪ§ЩшЖЈжавРееД§ВтзмЯпФкШнМгвдЩшЖЈЁЃ ЬсЪОЃКдаСњТпМЗжЮівЧSPIзмЯпЗжЮіФЃПщПЩЭЌЪБЗжЮіSPIжаЕФMOSIМАMISOЃЌЪЙгУЪБНіашЩшЖЈСНзщSPIзмЯпЗжЮіФЃПщМДПЩЁЃ |

| ВНжшЮх |

| |

| ЭъГЩЩшЖЈКѓЃЌШэМўФЃПщЛсНЋзмЯпФкЕФЗтАќЪ§жЕЯдЪОгкЦСФЛЩЯЁЃ ЬсЪОЃКдаСњПЦММТпМЗжЮівЧШэМўЛЙгаЦфЫќЧПДѓЙІФмПЩАяжњЪЙгУепНјаазмЯпЗжЮіЃЌШчЗтАќСаБэЯдЪОЁЂЪ§ОнЫббАЁЂТіВЈПэЖШЫббА….ЕШЕШЁЃ |

ЮяЦЗЧхЕЅ

жїЛњЃЌВтЪдЯпЃЌВтЪдЙДЃЌБЋГЇЕўЯпЃЌШэМў/ЫЕУїЪщЙтХЬЃЌБЃаоПЈЃЌаЏДјАќИївМЬзЁЃ